### **Features and Benefits**

- Low R<sub>DS(on)</sub> outputs

- Standby mode with zero current drain

- Small  $2 \times 2$  DFN package

- Crossover Current protection

- Thermal Shutdown protection

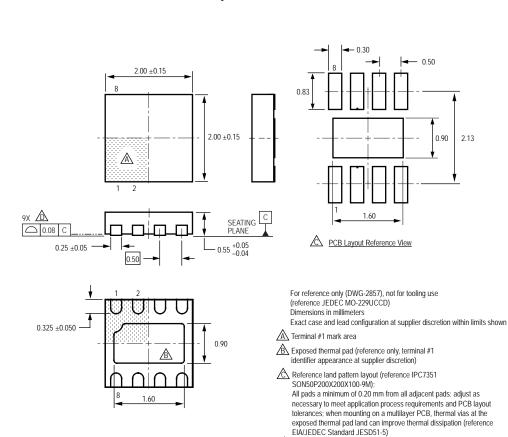

# Package: 8-contact DFN with Exposed Thermal Pad (suffix EE)

Not to scale

### Description

The A3910 is a dual half bridge motor driver, designed for low cost, low voltage battery operated power applications. The outputs are rated for operation up to 500 mA.

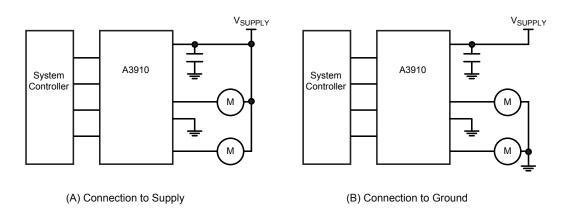

Direct control of high- and low-side drivers is implemented to allow either high-side or low-side PWM. The motor can be connected to either supply or GND. Using a MOS switch results in improved braking action for the motor, compared to implementation with simple clamp diode.

The A3910 is supplied in a 2 mm  $\times$  2 mm 8-contact DFN package (EE) with exposed thermal pad. The package is lead (Pb) free, with 100% matte tin leadframe plating.

### **Typical Application Diagram**

#### **Selection Guide**

| Part Number  | Packing*                    | Package                                   |

|--------------|-----------------------------|-------------------------------------------|

| A3910EEETR-T | 3000 pieces per 13-in. reel | 8-contact DFN<br>with exposed thermal pad |

\*Contact Allegro<sup>TM</sup> for additional packing options.

#### **Absolute Maximum Ratings\***

| Characteristic                | Symbol               | Notes               | Rating                      | Unit |

|-------------------------------|----------------------|---------------------|-----------------------------|------|

| Supply Voltage                | V <sub>BB</sub>      |                     | -0.3 to 5.5                 | V    |

| Logic Input Voltage Range     | V <sub>IN</sub>      |                     | -0.3 to 6                   | V    |

| Output Current                | I <sub>OUT</sub>     |                     | 500                         | mA   |

| Output Voltage                | V <sub>OUT</sub>     |                     | –0.3 to V <sub>BB</sub> + 1 | V    |

| Operating Ambient Temperature | T <sub>A</sub>       | E temperature range | -40 to 85                   | °C   |

| Maximum Junction Temperature  | T <sub>J</sub> (max) |                     | 150                         | °C   |

| Storage Temperature           | T <sub>stg</sub>     |                     | –55 to 150                  | °C   |

#### Thermal Characteristics may require derating at maximum conditions, see application information

| Characteristic             | Symbol | Test Conditions*                                                         | Value | Unit |

|----------------------------|--------|--------------------------------------------------------------------------|-------|------|

|                            |        | On 4-layer PCB based on JEDEC standard                                   | 49    | °C/W |

| Package Thermal Resistance |        | On 2-layer PCB based with 0.23 in. <sup>2</sup> exposed copper each side | 92    | °C/W |

\*Additional thermal information available on the Allegro website.

#### **Terminal List Table**

#### **Pin-out Diagram**

| HIN1 | [1]) | PAD | (8) | OUT1 |

|------|------|-----|-----|------|

| LIN1 | [2]) |     | (7) | VBB  |

| LIN2 | [3]) |     | (6) | GND  |

| HIN2 | [4]) |     | (5) | OUT2 |

|      |      |     |     |      |

| Number | Name | Function       |  |  |

|--------|------|----------------|--|--|

| 1      | HIN1 | Logic input    |  |  |

| 2      | LIN1 | Logic input    |  |  |

| 3      | LIN2 | Logic input    |  |  |

| 4      | HIN2 | Logic input    |  |  |

| 5      | OUT2 | Motor terminal |  |  |

| 6      | GND  | Ground         |  |  |

| 7      | VBB  | Input Supply   |  |  |

| 8      | OUT1 | Motor terminal |  |  |

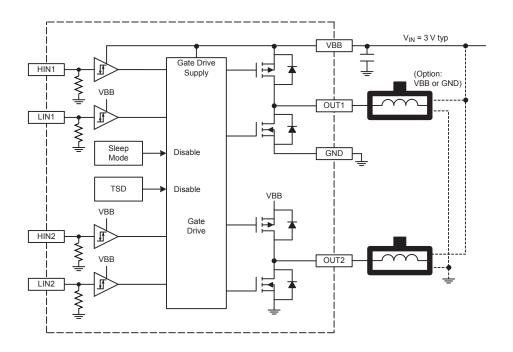

## **Functional Block Diagram**

### **ELECTRICAL CHARACTERISTICS**\* Valid at $T_A = 25^{\circ}C$ ; unless otherwise specified

| Characteristic               | Symbol              | Test Conditions                                  | Min.               | Тур. | Max. | Unit |

|------------------------------|---------------------|--------------------------------------------------|--------------------|------|------|------|

| VBB Supply Range             | V <sub>BB</sub>     |                                                  | 2.5                | _    | 5.5  | V    |

| VBB Supply Current           |                     | Both bridges, PWM = 50 kHz                       | -                  | 0.3  | 1    | mA   |

|                              | I <sub>BB</sub>     | Sleep mode (HIN1=HIN2=LIN1=LIN2=0V)              | -                  | <1   | 1    | μA   |

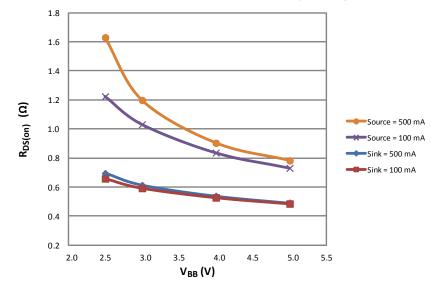

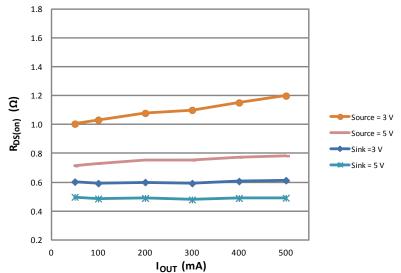

|                              |                     | Source driver, I = 400 mA, V <sub>BB</sub> = 3 V | -                  | 1.1  | 1.4  | Ω    |

| Output Driver On Desistance  |                     | Source driver, I = 400 mA, V <sub>BB</sub> = 5 V | -                  | 0.8  | 1    | Ω    |

| Output Driver On-Resistance  | R <sub>DS(on)</sub> | Sink driver, I = 400 mA, V <sub>BB</sub> = 3 V   | -                  | 0.5  | 0.65 | Ω    |

|                              |                     | Sink driver, I = 400 mA, V <sub>BB</sub> = 5 V   | -                  | 0.4  | 0.52 | Ω    |

| Input Logic Low Level        | VIL                 |                                                  | -                  | _    | 0.5  | V    |

| Input Logic High Level       | V <sub>IH</sub>     |                                                  | V <sub>BB</sub> /2 | _    | -    | V    |

| Input Hysteresis             | V <sub>HYS</sub>    |                                                  | 50                 | 150  | 300  | mV   |

| Logic Input Current          | I <sub>IN</sub>     | V <sub>IN</sub> = 3.3 V (Pulldown = 100 kΩ)      | -                  | 33   | 50   | μA   |

| Thermal Shutdown Temperature | T <sub>JTSD</sub>   | Temperature increasing                           | -                  | 165  | -    | °C   |

| Thermal Shutdown Hysteresis  | $\Delta T_{J}$      | Recovery = $T_{JTSD} - \Delta T_J$               | -                  | 15   | -    | °C   |

\*Specified limits are tested at a single temperature and assured over operating temperature range by design and characterization.

#### Logic Table

| HINx | LINx | OUTx              | Function Motor to Supply    | Function Motor to GND       |

|------|------|-------------------|-----------------------------|-----------------------------|

| 0    | 0    | Hi-Z <sup>1</sup> | Coast (Sleep <sup>2</sup> ) | Coast (Sleep <sup>2</sup> ) |

| 1    | 0    | High              | Brake                       | Drive                       |

| 0    | 1    | Low               | Drive                       | Brake                       |

| 1    | 1    | Hi-Z <sup>1</sup> | Coast                       | Coast                       |

<sup>1</sup>Hi-Z is high impedance.

<sup>2</sup>Sleep mode activated by all four inputs <100 mV.

## **Characteristic Performance**

Output On-Resistance versus Load Supply Voltage

Package EE, 8-Contact DFN with Exposed Thermal Pad

Copyright ©2013, Allegro MicroSystems, LLC

Allegro MicroSystems, LLC reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

<u>Allegro's products are not to be used in life support devices or systems, if a failure of an Allegro product can reasonably be expected to cause the failure of that life support device or system, or to affect the safety or effectiveness of that device or system.</u>

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, LLC assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.

For the latest version of this document, visit our website:

www.allegromicro.com